(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-211159

(P2005-211159A)

(43) 公開日 平成17年8月11日(2005.8.11)

(51) Int.Cl.<sup>7</sup>**A61B 1/04**

**HO4N 5/225**

F 1

A 6 1 B 1/04

H O 4 N 5/2253 7 O

Cテーマコード (参考)

4 C 0 6 1

5 C 0 2 2

審査請求 未請求 請求項の数 2 O L (全 10 頁)

(21) 出願番号

(22) 出願日特願2004-18897 (P2004-18897)

平成16年1月27日 (2004.1.27)

(71) 出願人 000005430

フジノン株式会社

埼玉県さいたま市北区植竹町1丁目324

番地

(74) 代理人 100098372

弁理士 緒方 保人

(72) 発明者 阿部 一則

埼玉県さいたま市北区植竹町1丁目324

番地 富士写真光機株式会社内

F ターム (参考) 4C061 CC06 GG11 JJ17 NN05 SS21

TT12 WW20

5C022 AA09 AC69

(54) 【発明の名称】電子内視鏡装置

## (57) 【要約】

【課題】画素数の異なる電子内視鏡を接続する場合でも解像度を低下させることなく、ハイビジョンテレビ方式の映像を観察しやすい状態で形成・表示する。

## 【解決手段】

C C D の画素数が異なる各種の電子内視鏡 1 0 を接続するプロセッサ装置 1 6 に、パソコン等の表示規格のデジタル映像信号を形成しこれを作動信号として出力する D V I 回路 2 8 を設け、このD V I 回路 2 8 の出力側にハイビジョン方式変換器 3 7 を着脱自在に接続する。このハイビジョン方式変換器 3 7 では、H D T V 信号変換部 4 4 にて、入力されたデジタル映像信号の画素数を検出してハイビジョンテレビ信号へ変換するが、このとき表示画素数調整回路 4 7 は、異なる画素数の映像信号を一定の例えは S X G A 規格の表示画素数に電子変倍する。また、上記表示画素数調整回路 4 7 は、プロセッサ装置へ設けることもできる。

【選択図】図 1

**【特許請求の範囲】****【請求項 1】**

被観察体を撮像するための固体撮像素子の画素数が異なる各種の電子内視鏡をプロセッサ装置に接続可能に構成し、上記固体撮像素子で得られた信号からアナログ映像信号とデジタル映像信号を形成する電子内視鏡装置において、

上記プロセッサ装置に配置され、上記固体撮像素子の画素数に対応させかつ外部コンピュータ用表示規格に合わせたデジタル映像信号を形成すると共に、このデジタル映像信号をパラレル・シリアル変換し、差動信号として出力する差動信号出力部と、

この差動信号出力部に対し着脱自在に接続され、この差動信号出力部から入力した差動信号に基づいてデジタル映像信号の画素数を検出する画素数検出回路を有し、映像信号をハイビジョンテレビ信号へ変換し出力するハイビジョン方式変換器と、

このハイビジョン方式変換器に配置され、上記画素数検出回路の出力に基づいた電子的変倍によって映像信号の画素数を一定の表示画素数に合わせる表示画素数調整回路と、を設けたことを特徴とする電子内視鏡装置。10

**【請求項 2】**

被観察体を撮像するための固体撮像素子の画素数が異なる各種の電子内視鏡をプロセッサ装置に接続可能に構成し、上記固体撮像素子で得られた信号からアナログ映像信号とデジタル映像信号を形成する電子内視鏡装置において、

上記プロセッサ装置に配置され、電子的変倍によって映像信号の画素数を一定の表示画素数に合わせる表示画素数調整回路と、20

上記プロセッサ装置に配置され、外部コンピュータ用表示規格に合わせたデジタル映像信号を形成すると共に、このデジタル映像信号をパラレル・シリアル変換し、差動信号として出力する差動信号出力部と、

この差動信号出力部に対し着脱自在に接続され、一定の表示画素数とされた映像信号をハイビジョンテレビ信号へ変換し出力するハイビジョン方式変換器と、設けたことを特徴とする電子内視鏡装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は電子内視鏡装置、特に固体撮像素子の画素数の異なる各種の電子内視鏡が使用される環境で、ハイビジョンテレビ方式のモニタへも被観察体映像を出力することができる電子内視鏡装置の構成に関する。30

**【背景技術】****【0002】**

電子内視鏡装置は、固体撮像素子である C C D ( Charge Coupled Device ) 等を電子内視鏡(電子スコープ)の先端部に搭載しており、この C C D は光源装置からの光の照明に基づいて被観察体を撮像する。そして、この電子内視鏡の C C D で得られた撮像信号をプロセッサ装置へ出力し、このプロセッサ装置で映像処理を施すことにより、被観察体の映像をモニタへ表示したり、静止画等を記録装置へ記録したりできるものである。

**【0003】**

一般に、上記の被観察体映像は、標準テレビジョン方式である N T S C 方式用モニタ(縦横比 3 : 4)に表示されるが、例えば特開平 4 - 253830 号公報に示されるように、走査線数が約 2 倍となる高品位のハイビジョンテレビ( H D T V )方式のモニタ(縦横比 9 : 16)に被観察体映像を表示することも試みられている。電子内視鏡装置では、C C D の出力信号から通常の N T S C 方式の信号(アナログ信号)が形成されるので、この N T S C 信号をハイビジョンテレビ信号へ変換することが行われる。40

**【0004】**

一方、電子内視鏡装置で得られた被観察体の静止画(デジタル信号)は、パソコン用コンピュータ(パソコン)等のファイリング装置で記録媒体に記録し、後にパソコン用モニタへ表示して観察することが行われており、同時に C C D においては高解像度となる高画50

素数のものが用いられる傾向となっている。

【特許文献1】特開平4-253830号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

上述のように、近年では固体撮像素子であるCCDが高解像度化、高画素数化されていることから、ハイビジョンテレビ方式による映像表示おいても、従来と比較すると画質が向上した被観察体映像を観察できるという利点があるが、上述のようにNTSC信号をハイビジョンテレビ信号へ変換するのでは、NTSC映像信号の解像度に制限され、高画質化されたCCDの解像度を十分に生かすことができないという問題がある。

10

【0006】

また、電子内視鏡には上述のように異なる画素数のCCDが搭載されており、このCCD画素数の相違や高画素数化の変遷に対応してハイビジョンテレビ信号への変換回路をプロセッサ装置内に配置し又は更新(交換)するのでは、コスト的に無駄があり、装置が高価になるという問題がある。

更に、医療現場で使用される機器には、EMC(Electro-Magnetic Compatibility)や電気安全性について厳しい規格が要求されており、ハイビジョンテレビ信号への変換のために、パソコン等の専用の大きな装置において上記の医療用の規格が満たされるようにすることも非現実的である。

20

【0007】

本発明は上記問題点に鑑みてなされたものであり、その目的は、パーソナルコンピュータ等へ供給するためにデジタル処理した映像出力を利用し、画素数の異なる固体撮像素子を搭載する電子内視鏡を接続する場合でも、解像度を低下させることなく、ハイビジョンテレビ方式の映像を簡単な構成かつ低コストにて得ることができ、また観察しやすい状態で表示することが可能となる電子内視鏡装置を提供することにある。

【課題を解決するための手段】

【0008】

上記目的を達成するために、請求項1に係る発明は、被観察体を撮像するための固体撮像素子の画素数が異なる各種の電子内視鏡をプロセッサ装置に接続可能に構成し、上記固体撮像素子で得られた信号からアナログ映像信号とデジタル映像信号を形成する電子内視鏡装置において、上記プロセッサ装置に配置され、上記固体撮像素子の画素数に対応させかつ外部コンピュータ用表示規格に合わせたデジタル映像信号を形成すると共に、このデジタル映像信号をパラレル・シリアル変換し、差動信号として出力する差動信号出力部と、この差動信号出力部に対し着脱自在に接続され、この差動信号出力部から入力した差動信号に基づいてデジタル映像信号の画素数(画素数サイズで、画像サイズでもある)を検出する画素数検出回路を有し、映像信号をハイビジョンテレビ信号へ変換し出力するハイビジョン方式変換器と、このハイビジョン方式変換器に配置され、上記画素数検出回路の出力に基づいた電子的変倍(拡大又は縮小)によって映像信号の画素数を一定の表示画素数(表示画像サイズ)に合わせる表示画素数調整回路と、を設けたことを特徴とする。

30

また、請求項2に係る発明は、被観察体を撮像するための固体撮像素子の画素数が異なる各種の電子内視鏡をプロセッサ装置に接続可能に構成し、上記固体撮像素子で得られた信号からアナログ映像信号とデジタル映像信号を形成する電子内視鏡装置において、上記プロセッサ装置に配置され、電子的変倍によって映像信号の画素数を一定の表示画素数に合わせる表示画素数調整回路と、上記プロセッサ装置に配置され、外部コンピュータ用表示規格に合わせたデジタル映像信号を形成すると共に、このデジタル映像信号をパラレル・シリアル変換し、差動信号として出力する差動信号出力部と、この差動信号出力部に対し着脱自在に接続され、一定の表示画素数とされた映像信号をハイビジョンテレビ信号へ変換し出力するハイビジョン方式変換器と、設けたことを特徴とする。

40

【0009】

上記の構成によれば、固体撮像素子であるCCDには各種の画素(ピクセル)数を持つ

50

ものが存在することから、パーソナルコンピュータ等へ出力するための差動信号出力部（例えばDVI）では、640（水平方向）×480（垂直方向）の画素のVGA（Video Graphics Array）、1024×768画素のXGA（eXtended Graphics Array）、1280×960画素、1280×1024画素のSXGA（Super XGA）等の規格に合わせたデジタル映像信号が形成され、この映像信号がパラレル・シリアル変換された後、差動信号としてパソコン用モニタ等へ出力される。この差動信号であるデジタル映像信号がハイビジョン方式変換器へ供給されると、その映像信号の画素数が検出され、この検出画素数に基づいて一定の表示画素数のハイビジョンテレビ信号が形成される。即ち、表示画素数調整回路では、例えばXGA、VGA規格の大きさ（画素数）の映像が電子的に拡大され、1280×960の画素数サイズ映像として形成され、CCDの全ての画素情報を生かす形でハイビジョン信号が得られる。従って、このハイビジョン方式変換器をプロセッサ装置に接続するだけで、ハイビジョン用モニタにて被観察体映像（動画又は静止画）を観察することができると共に、CCDの画素数が異なる場合でも、同一の画素数サイズ（画面領域）で表示された被観察体映像を観察することが可能となる。また、この映像はハイビジョン用記録装置に記録することができる。

10

## 【0010】

上記請求項2の発明によれば、表示画素数調整回路がプロセッサ装置に設けられており、差動信号出力部に入力される前に表示画素数が同一となる映像が形成される。一方、ハイビジョン方式変換器では、入力される画素数が予め分かれているので、この画素数の検出をすることなく、ハイビジョン信号への変換が行われる。この場合も、ハイビジョンモニタ上の同一の大きさの画素数（画面領域）で被観察体を観察することができる。

20

## 【発明の効果】

## 【0011】

本発明の電子内視鏡装置のハイビジョン方式変換器によれば、デジタル映像をパーソナルコンピュータ等へ供給するための差動信号出力部出力をを利用して、CCDで採用される画素数（解像度）が異なる電子内視鏡を接続する場合でも、CCDが持つ解像度を低下させることなく、ハイビジョンテレビ方式の映像を簡単な構成かつ低コストで形成し、また同一サイズの画素数で被観察体をハイビジョンモニタに表示し、観察することができる。そして、この映像はハイビジョン用の記録装置に記録することも可能となる。従って、多くの内視鏡映像（動画又は静止画）を観察するルーチン検査等では、観察、診断が迅速かつ容易になるという効果がある。更に、このビジョン方式変換器を、医療現場で要求されるEMCや電気安全性の規格を満たしたアダプター装置とすることにより、医療現場におけるハイビジョン映像の観察が容易になるという利点がある。

30

一方、請求項2の発明によれば、表示画素数調整回路をプロセッサ装置へ配置したので、ハイビジョン方式変換器では入力される映像信号の画素数が一定となることから、この画素数（画像サイズ）の検出が不要になるという利点がある。

## 【発明を実施するための最良の形態】

## 【0012】

本発明の表示画素数調整回路は、ハイビジョン方式変換器の中に配置する（実施例1）だけでなく、プロセッサ装置の中に配置することもできる（実施例2）。

40

## 【実施例1】

## 【0013】

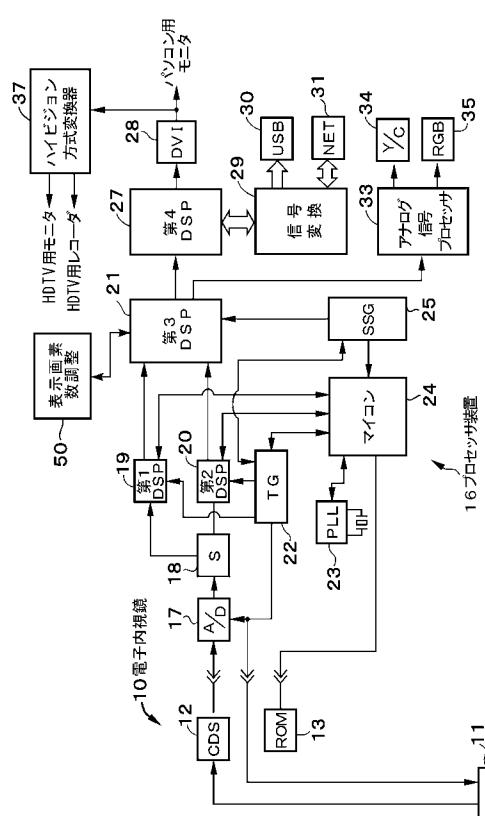

図1乃至図3には、実施例1に係る電子内視鏡装置の構成が示されており、まず図3に基づいて全体の構成を説明する。図3において、電子内視鏡（電子スコープ）10には、その先端部に固体撮像素子であるCCD11が設けられており、このCCD11としては、40万画素、80万画素、131万画素等、各種のものが搭載される。また、このCCD11から出力された撮像信号をサンプリングする関連二重サンプリング（CDS）回路12及び電子内視鏡10の識別情報や映像処理情報等を格納するメモリ（EEPROM）13等が設けられる。なお、この電子内視鏡10には、図示していない光源装置の光がライトガイドを介して供給されており、先端部から照明光を出力することにより被観察体が

50

上記 C C D 1 1 で撮像される。そして、上述した画素数（若しくはその画素数に対応した C C D の転送方式）の異なる C C D 1 1 を搭載する各種の電子内視鏡 1 0 は、プロセッサ装置 1 6 に着脱自在に接続可能となっている。

#### 【 0 0 1 4 】

このプロセッサ装置 1 6 には、A / D 変換器 1 7 、映像信号に対し各種の信号処理をするための第 1 D S P (デジタル信号プロセッサ) 1 9 、第 2 D S P 2 0 及び第 3 D S P 2 1 、上記 D S P 1 9 , 2 0 の何れかを選択するためのセレクタ (S) 1 8 、上記 C C D 1 1 から第 1 及び第 2 D S P 1 9 , 2 0 までの回路に対し同期信号やタイミング信号を供給するタイミングジェネレータ 2 2 、水晶発振器を有する P L L 回路 2 3 、各種の制御を実行するマイコン 2 4 、上記第 3 D S P 2 1 等に同期信号やタイミング信号を供給するための同期信号発生回路 (S S G) 2 5 が設けられる。10

#### 【 0 0 1 5 】

また、上記第 3 D S P 2 1 の後段には、デジタル映像信号を形成するための第 4 D S P 2 7 、そして D V I (Digital Visual Interface) 回路 2 8 が設けられており、この D V I 回路 2 8 は、パソコン用モニタ等へ出力するための表示規格、例えば  $640 \times 480$  (VGA) 、 $1024 \times 768$  (XGA) 、 $1280 \times 960$  、 $1280 \times 1024$  (SXGA) 等に対応した映像信号を形成し、その後にパラレル - シリアル変換し、このシリアル信号を差動信号としてパソコン用モニタやファイリング装置等へ出力する。なお、上記 D V I は、D D W G (Digital Display Working Group) が設定した高速スピードのディスプレイ用インターフェースで、データフォーマットに T M D S (Transition Minimized Differential Signaling) を採用する。一方、上記第 4 D S P 2 7 には、信号変換回路 2 9 を介して U S B 出力部 3 0 やネット出力部 3 1 が設けられており、この U S B 出力部 3 0 、ネット出力部 3 1 からはそれぞれの出力形態に合わせた信号が出力される。更に、上記第 3 D S P 2 1 の後段には、デジタル処理された映像信号をアナログ信号へ変換するアナログ信号プロセッサ 3 3 、輝度 (Y) 信号と色差 (C) 信号を出力する Y / C 信号出力部 3 4 、R (赤) , G (緑) , B (青) の信号を出力する R G B 出力部 3 5 が設けられる。20

#### 【 0 0 1 6 】

そして、上記の D V I 回路 2 8 の出力部（端子）に着脱自在に接続する形で、ハイビジョン方式変換器 3 7 が設けられ、このハイビジョン方式変換器 3 7 の出力が H D T V 用モニタや H D T V 用レコーダへ接続される。なお、図 3 の構成においてプロセッサ装置 1 6 内の回路として説明したものの一部を、電子内視鏡 1 0 側に配置する構成にすることができる。30

#### 【 0 0 1 7 】

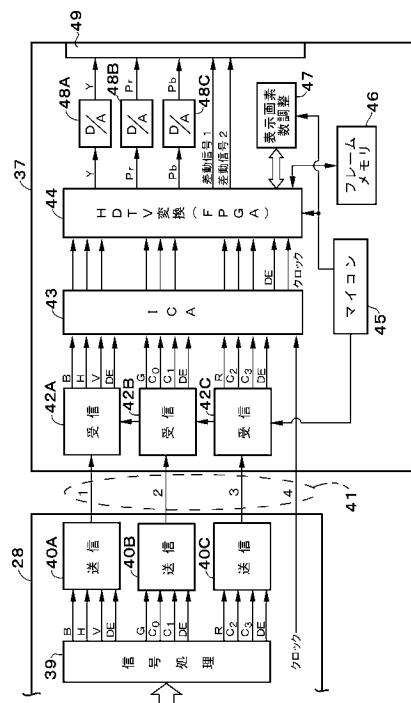

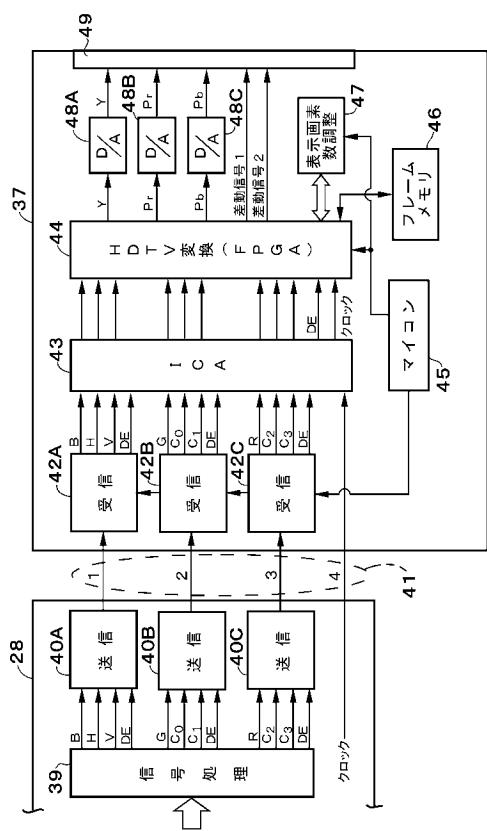

図 1 には、上記 D V I 回路 2 8 とハイビジョン方式変換器 3 7 内の詳細な構成が示されており、D V I 回路 2 8 では、上述した各表示規格の映像を形成する信号処理部 3 9 や R G B の信号、同期信号及び制御信号等を送信するための送信部 4 0 A , 4 0 B , 4 0 C が設けられる。この D V I 回路 2 8 は、シリアル伝送ケーブル 4 1 を介してハイビジョン方式変換器 3 7 に接続され、このハイビジョン方式変換器 3 7 には、上記 3 つの送信部 4 0 A , 4 0 B , 4 0 C に対応した受信部 4 2 A , 4 2 B , 4 2 C 、I C A (Inter Channel Alignment) 部 4 3 、映像の画素数を検出してハイビジョンテレビ信号を形成する H D T V (ハイビジョンテレビ) 信号変換部 (F P G A - Filed Programmable Gate Array 回路) 4 4 、各種の制御を実行するマイコン 4 5 、入力した映像信号を一時的に記憶するフレームメモリ 4 6 が設けられる。40

#### 【 0 0 1 8 】

そして、上記 H D T V 信号変換部 4 4 に、上記の  $640 \times 480$  (VGA) 、 $1024 \times 768$  (XGA) 、 $1280 \times 960$  、 $1280 \times 1024$  (SXGA) の規格の映像を電子的に拡大（又は縮小）することによって一定の表示画素数、例えば SXGA の画素数に合わせるための表示画素数調整回路 4 7 が接続される。また、この H D T V 信号変換部 4 4 とコネクタ 4 9 との間には、輝度 (Y) 信号、色差信号である P r , P b 信号に対50

応して D / A 変換器 48A, 48B, 48C が設けられる。

【0019】

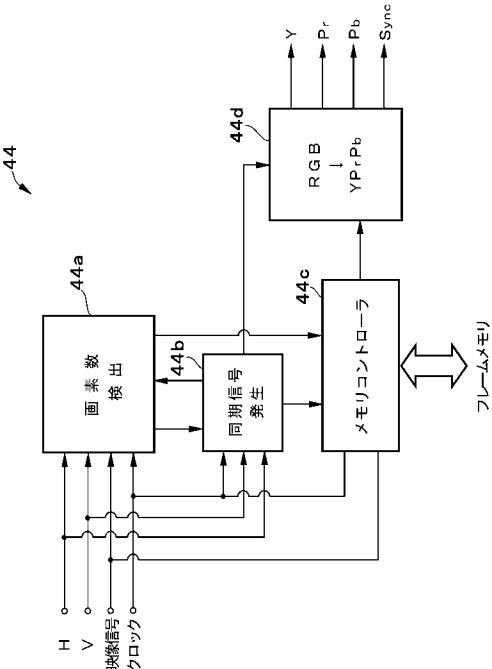

図2には、上記HDTV信号変換部44内の構成が示されており、このHDTV信号変換部44には、水平同期信号(H)、垂直同期信号(V)、映像信号及びクロック信号を入力して映像信号の画素数(画像サイズ)を検出する画素数検出回路44a、ハイビジョン映像形成のための同期信号発生回路44b、上記フレームメモリ46に対し映像信号の書き込み及び読み出しを制御するメモリコントローラ44c、このメモリコントローラ44cから出力されたRGB信号をハイビジョン映像であるY, Pr, Pb信号に変換する信号変換器44dが設けられる。

【0020】

実施例1は以上の構成からなり、その作用を図4及び図5を参照しながら説明する。まず、この電子内視鏡装置では、図3のCCD11にて被観察体内が撮像され、その撮像信号はCDS回路12にてサンプリングされ、A/D変換器17でデジタル信号へ変換された後に、セレクタ18へ供給される。このセレクタ18では、接続された電子内視鏡10の種類に応じて第1DSP19と第2DSP20の何れかを選択する。例えば、電子内視鏡10とプロセッサ装置16との通信によってマイコン24がメモリ13内の情報を読み取ることにより、CCD11の画素数(若しくはその画素数に対応したCCDの転送方式)に応じ、第1DSP19(インターラインスキャンの場合)か、第2DSP20(プログレッシブスキャンの場合)を選択する。

【0021】

この第1DSP19又は第2DSP20と第3DSP21では、各種の映像処理が施されることになり、この第3DSP21の出力は、第4DSP27とアナログ信号プロセッサ33へ供給される。この第4DSP27では、デジタル出力のための映像信号が形成されており、この映像信号は、信号変換回路29、USB出力部30及びネット出力部31を介して外部へ出力されると共に、DVI回路28を介してパソコン用モニタ等に出力することができる。一方、上記アナログ信号プロセッサ33では、アナログ出力のための映像信号が形成され、Y/C信号出力部34を介してY信号とC信号が出力されると共に、RGB出力部35を介してR, G, Bの各色信号が出力される。

【0022】

一方、上記DVI回路28の出力がハイビジョン方式変換器37へ供給されると、このハイビジョン方式変換器37ではハイビジョンテレビ信号が形成される。即ち、図1に示されるDVI回路28の信号処理部39によって、CCD11の画素数に対応した例えば $640 \times 480$ (VGA)、 $1024 \times 768$ (XGA)、 $1280 \times 960$ 、 $1280 \times 1024$ (SXGA)等の表示規格の映像信号が形成される。そして、この信号処理部39から出力されたパラレル信号[B(青), G(緑), R(赤), H(水平同期信号), V(垂直同期信号), C<sub>0</sub>, C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub>(制御信号)等]は、送信部40A~40Cでシリアル信号に変換され、ケーブル41を介してハイビジョン方式変換器37へ出力される。図1のように、送信部40Aから送信されたB信号とH, V等の信号は受信部42Aで、送信部40Bから送信されたG信号とその他の信号は受信部42Bで、送信部40Cから送信されたR信号とその他の信号は受信部42Cで受信される。これらの受信部42A~42Cでは、シリアル信号が元のパラレル信号へ変換され、この信号がIICA回路43を介してHDTV信号変換部(FPGA)44へ供給される。

【0023】

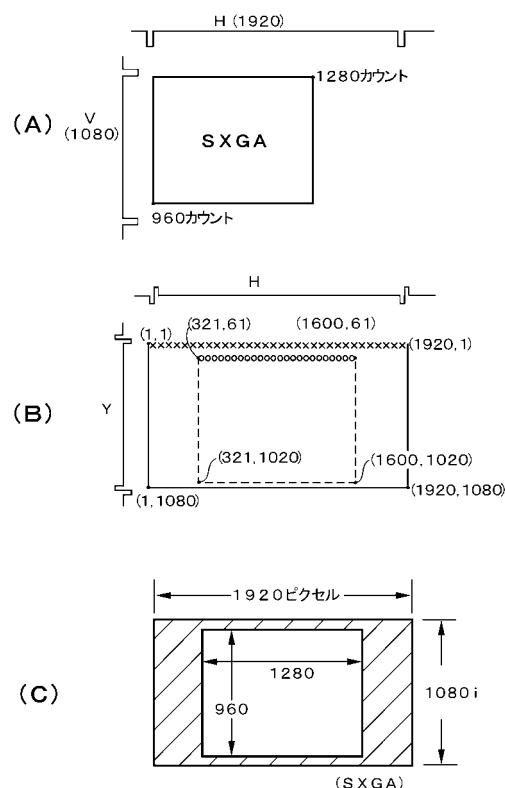

このHDTV信号変換部44では、入力された映像信号が図2のメモリコントローラ44cを介してフレームメモリ46に格納されると同時に、画素数検出回路44aにて入力映像信号の画素数が例えば水平同期信号や垂直同期信号によって検出される。即ち、図4(A)に示されるように、ハイビジョン方式の水平同期信号(H)は1920画素分、垂直同期信号(V)は1080画素分の長さとなるが、例えば変換器37へ入力された映像信号の水平同期信号によって1280の水平画素が検出(カウント)されたとき、又は垂直同期信号によって960の垂直画素が検出されたときは、 $1280 \times 960$ の映像(画

10

20

30

40

50

像)であると判断される。同様に、1024の水平画素又は768の垂直画素が検出されたときは $1024 \times 768$ のXGA規格の映像、640の水平画素又は480の垂直画素が検出されたときは $640 \times 480$ のVGA規格の映像、1280の水平画素又は1024の垂直画素が検出されたときは $1280 \times 1024$ のSXGAの映像であると判断される。そして、表示画素数調整回路47にて、異なる画素数の映像が一定の $1280 \times 960$ の画素数に変換されることになるが、これと同一の画素数である場合[図4(A)]は、この表示画素数の調整は行われない。

#### 【0024】

次に、上記画素数の検出結果が同期信号発生回路44bとメモリコントローラ44cに供給されることにより、メモリコントローラ44cでは画素数に応じてフレームメモリ46からの映像信号の読み出し制御が行われる。上記 $1280 \times 960$ 画素(SXGA)の映像の場合は、図4(B)に示されるように、垂直方向の1~60までは全ての水平画素に黒色を割り当て、垂直方向61番目については、水平方向の321~1600において上記 $1280 \times 960$ 画素の映像信号を割り当てるというようにして、(321, 61)、(1600, 61)、(321, 1020)、(1600, 1020)の画素で囲まれる範囲の映像信号(RGB信号)が読み出される。その他の画素には、黒色が割り当てられる。そして、信号変換器44dでは、RGB信号がY, Pr, Pb信号へ変換され、このY, Pr, Pb信号と同期信号がHDTV用モニタやHDTV用レコーダへ出力される。このようにして、図4(C)に示されるように、HDTV用モニタには、 $1280 \times 960$ 画素の被観察体映像を中心領域に配置したハイビジョン映像、即ち $1920 \times 1080$ i(インターレース)の画素の映像(フォーマットD<sub>4</sub>)が表示される。

#### 【0025】

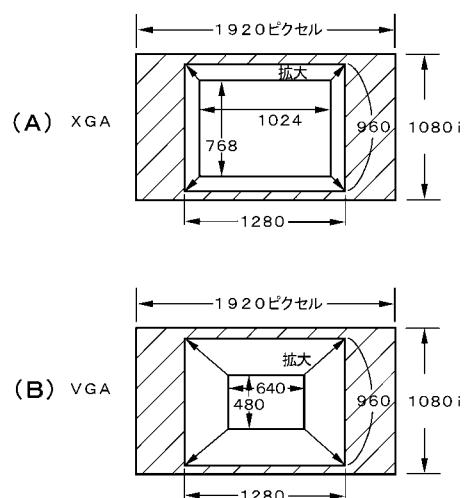

図5(A)には、XGA規格の $1024 \times 768$ 画素の映像が検出された場合のハイビジョン映像が示されており、この場合は、表示画素数調整回路47にて、 $1024 \times 768$ 画素の映像(画像)がSXGAの $1280 \times 960$ 画素数サイズに拡大される。この拡大処理は、従来の電子内視鏡装置で用いられる電子拡大処理回路の場合と同様に水平及び垂直方向の画素データ補間処理等によって行われ、この拡大映像がフレームメモリ46へ順次書き込まれる。そして、上記の図4(B)の場合と同様の読み出しを行うことにより、HDTV用モニタに $1280 \times 960$ 画素の大きさの被観察体映像を中心領域に配置したハイビジョン映像が表示される。

#### 【0026】

図5(B)には、VGA規格の $640 \times 480$ 画素の映像が検出された場合のハイビジョン映像が示されており、この場合は、表示画素数調整回路47にて、 $640 \times 480$ 画素数の映像が $1280 \times 960$ 画素数に拡大処理される。この結果、HDTV用モニタに $1280 \times 960$ 画素の大きさの被観察体映像を中心領域に配置したハイビジョン映像が表示され、実施例では、如何なる画素数の被観察体映像であっても、一定のSXGA規格の画素数でハイビジョン用モニタに表示することが可能となる。

#### 【実施例2】

#### 【0027】

実施例2は、図3に示されるように、電子変倍処理を行う表示画素数調整回路50をプロセッサ装置16内に配置したものであり、この表示画素数調整回路50は、例えば画像メモリを有し、第3DSP21に接続される。即ち、この表示画素数調整回路50では、第3DSP21で形成された映像信号が画像メモリに一旦格納され、この画像メモリから読み出した映像信号が電子変倍処理によって一定の画素数、例えばSXGAの画素数に拡大され、第4DSP27へ出力される。

#### 【0028】

実施例1の場合と同様に、 $1280 \times 960$ 画素の映像については電子拡大が行われず、XGA規格の映像について、図5(A)に示したように $1024 \times 768$ の画素数が $1280 \times 960$ の画素数、VGA規格の画像については、図5(B)に示したように $640 \times 480$ の画素数が $1280 \times 960$ の画素数へ拡大される。このようにして表示画素

10

20

30

40

50

数が統一された映像信号は、第4DSP27、DVI回路28を介してハイビジョン方式変換器37へ供給され、ここでは図4(B)のようにハイビジョン信号へ変換される。この結果、画素数の異なるCCD11で撮影された被観察体映像であっても、ハイビジョン用モニタにおいて同一の画素数(画面領域)で表示し、観察することが可能となる。

**【0029】**

なお、上記実施例1及び2では、XGA等の他の規格の画素数に変換し統一するようにもよいし、上記表示画素数調整回路47,50にて画素データの間引き等に基づく画素数縮小処理を行うことにより、統一する画素数サイズをCCDの画素数よりも小さな画素数に設定することも可能である。

**【画面の簡単な説明】**

10

**【0030】**

【図1】本発明の実施例1に係る電子内視鏡装置のDVI回路及びハイビジョン方式変換器の構成を示す回路ブロック図である。

【図2】図1のハイビジョン方式変換器内におけるHDTV信号変換部の構成を示す図である。

**【図3】実施例1及び2の電子内視鏡装置の全体構成を示す回路ブロック図である。**

【図4】実施例のハイビジョン方式変換器で行われる1280×960の映像信号の画素数検出[図(A)]、ハイビジョンテレビ信号への変換及び表示状態[図(B), (C)]を示す説明図である。

【図5】実施例のハイビジョン方式変換器で形成されるXGA規格映像信号のハイビジョン用モニタでの表示状態[図(A)]及びVGA規格映像信号のハイビジョン用モニタでの表示状態[図(B)]を示す説明図である。

20

**【符号の説明】**

**【0031】**

30

- 10 ... 電子内視鏡、 16 ... プロセッサ装置、

- 24, 45 ... マイコン、 27 ... 第4DSP、

- 28 ... DVI回路(差動信号出力部)、

- 37 ... ハイビジョン方式変換器、

- 44 ... HDTV(ハイビジョンテレビ)信号変換部、

- 44a ... 画素数検出回路、

- 44c ... メモリコントローラ、

- 46 ... フレームメモリ、

- 47, 50 ... 表示画素数調整回路。

【図1】

【図2】

【図3】

【図4】

【図5】

|                |                                                                                                                                                                                                                                                                                                                                             |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | <无法获取翻译>                                                                                                                                                                                                                                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">JP2005211159A5</a>                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2006-11-30 |

| 申请号            | JP2004018897                                                                                                                                                                                                                                                                                                                                | 申请日     | 2004-01-27 |

| [标]申请(专利权)人(译) | 富士写真光机株式会社                                                                                                                                                                                                                                                                                                                                  |         |            |

| 申请(专利权)人(译)    | 富士公司                                                                                                                                                                                                                                                                                                                                        |         |            |

| [标]发明人         | 阿部一則                                                                                                                                                                                                                                                                                                                                        |         |            |

| 发明人            | 阿部 一則                                                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号         | A61B1/04 H04N5/225                                                                                                                                                                                                                                                                                                                          |         |            |

| CPC分类号         | A61B1/05                                                                                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | A61B1/04.370 H04N5/225.C                                                                                                                                                                                                                                                                                                                    |         |            |

| F-TERM分类号      | 4C061/CC06 4C061/GG11 4C061/JJ17 4C061/NN05 4C061/SS21 4C061/TT12 4C061/WW20 5C022 /AA09 5C022/AC69 4C161/CC06 4C161/GG11 4C161/JJ17 4C161/NN05 4C161/SS21 4C161/TT12 4C161/WW20 5C122/DA26 5C122/EA47 5C122/EA56 5C122/EA70 5C122/FC00 5C122/FE03 5C122 /FG03 5C122/FH07 5C122/FH11 5C122/GE03 5C122/HA34 5C122/HA42 5C122/HA88 5C122/HB05 |         |            |

| 其他公开文献         | JP2005211159A                                                                                                                                                                                                                                                                                                                               |         |            |

**摘要(译)**

要解决的问题：即使连接具有不同像素数的电子内窥镜，也能够在不降低分辨率的情况下在易于观察的状态下形成和显示高清晰度电视系统的图像。— 的不同的连接的各种电子内窥镜10的像素处理器单元16的CCD数，所提供的DVI电路28，以形成的显示标准的数字视频信号，诸如个人计算机，并将其作为致动信号，该DVI电路28高清晰度系统转换器37可拆卸地连接到高视觉系统转换器37的输出侧。在HDTV标准转换器37在HDTV信号转换单元44，而是由检测像素输入数字视频信号的数目被转换成高清晰度电视信号，时间显示像素数调节电路47，不同的像素的数目例如，对于SXGA标准的固定数量的显示像素的视频信号。另外，显示像素数量调整电路47可以设置在处理器设备中。点域1